题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

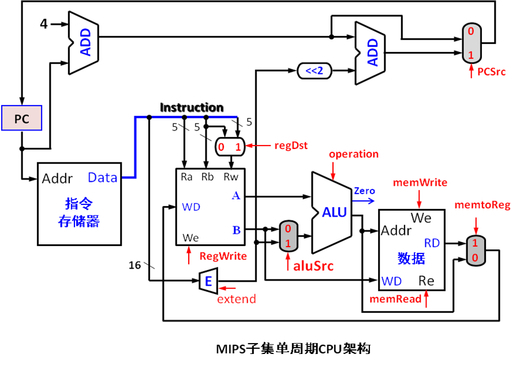

某型MIPS32指令架构的单周期CPU,其数据通路结构如下图 执行指令sub rd, rs, rt 时,应由控制器产生的控制信号PCSrc、regDst、aluSrc、memtoReg、RegWrite分别是() (单选)

执行指令sub rd, rs, rt 时,应由控制器产生的控制信号PCSrc、regDst、aluSrc、memtoReg、RegWrite分别是() (单选)

A.0、1、0、0、1

B.1、1、0、0、0

C.1、0、1、0、1

D.0、1、0、1、0

参考答案

参考答案

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

网友提供的答案

网友提供的答案

- · 有4位网友选择 D,占比36.36%

- · 有4位网友选择 A,占比36.36%

- · 有2位网友选择 B,占比18.18%

- · 有1位网友选择 C,占比9.09%