题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

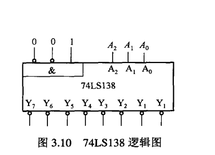

集成3-8译码器74LS138逻辑图如图3.10所示,要求用此3-8译码器和适当的逻辑门(规定与非门)设计一

集成3-8译码器74LS138逻辑图如图3.10所示,要求用此3-8译码器和适当的逻辑门(规定与非门)设计一个全减器;设Ai为被减数,Bi为减数,低位向该位的借位为小差为Di向高位借位为Ji+1.

(1)列出全减器真值表;(2)写出函数逻辑表达式;(3)画出实现逻辑电路图.

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

集成3-8译码器74LS138逻辑图如图3.10所示,要求用此3-8译码器和适当的逻辑门(规定与非门)设计一个全减器;设Ai为被减数,Bi为减数,低位向该位的借位为小差为Di向高位借位为Ji+1.

(1)列出全减器真值表;(2)写出函数逻辑表达式;(3)画出实现逻辑电路图.

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

更多“集成3-8译码器74LS138逻辑图如图3.10所示,要求用此3-8译码器和适当的逻辑门(规定与非门)设计一”相关的问题

更多“集成3-8译码器74LS138逻辑图如图3.10所示,要求用此3-8译码器和适当的逻辑门(规定与非门)设计一”相关的问题

3线-8线译码器74LS138如图3所示,当要实现逻辑功能 ,可以将74LS138的()输出管脚做与非运算得到。

,可以将74LS138的()输出管脚做与非运算得到。

A、

B、

C、

D、

E、

F、

G、

H、

10 用集成译码器74LS138和与非门实现下列逻辑函数:

(1)F1(A,B,C)=∑m(2,4,5,7)

(2)F2=A非BC+B非C非

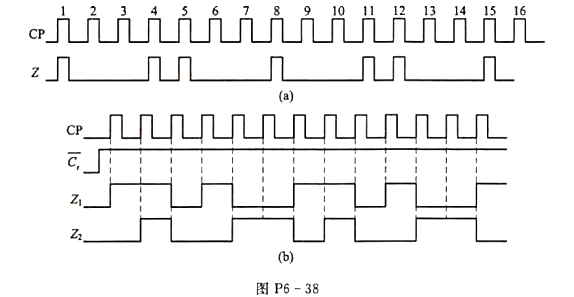

给出74LS161、74LS194、3-8译码器(74LS138)、4选1数据选择器,试设计下列电路:

(1) 波形发生器,要求输出波形如图P6-38(a)所示。

(2)双序列码发生器,要求其输出波形如图P6-38(b)所示。

(3)八路脉冲发生器。

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“简答题”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!