题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

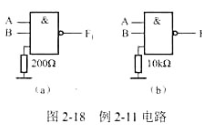

在右侧图中所示的逻辑门电路中,当输入端A=1,B=0时,P和Q端输出的逻辑值分别是()。

A.0,0

B. 0,1

C. 1,0

D. 1,1

参考答案

参考答案

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

网友提供的答案

网友提供的答案

- · 有3位网友选择 B,占比33.33%

- · 有2位网友选择 C,占比22.22%

- · 有2位网友选择 A,占比22.22%

- · 有2位网友选择 D,占比22.22%

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.0,0

B. 0,1

C. 1,0

D. 1,1

参考答案

参考答案

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

网友提供的答案

网友提供的答案

更多“在右侧图中所示的逻辑门电路中,当输入端A=1,B=0时,P和Q端输出的逻辑值分别是()。”相关的问题

更多“在右侧图中所示的逻辑门电路中,当输入端A=1,B=0时,P和Q端输出的逻辑值分别是()。”相关的问题

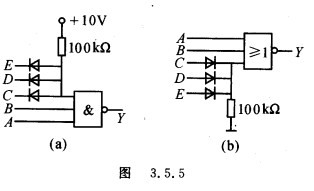

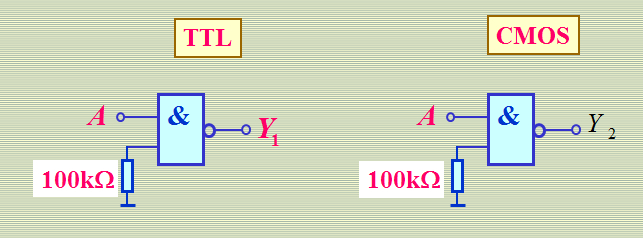

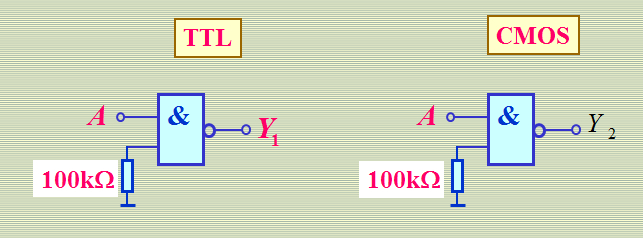

在CMOS门电路中,有时采用图3.5.5所示的方法扩展输入端。试分析图中(a),(b)所示电路的逻辑功能,写出Y的逻辑表达式。假定VDD=10 V,二极管的正向导通压降VD=0.7 V。

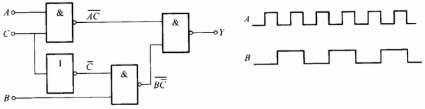

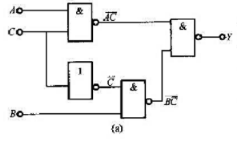

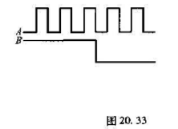

在图20.31(a)的门电路中,当控制端有C=1和C=0两种情况时,试求输出Y的逻辑式和波形,并说明该电路的功能。输入A和B的波形如图中所示。

在图20.37(a)的门电路中,当控制端C=1和C=0两种情况时,试求输出Y的逻辑式和波形,并说明该电路的功能。输入A和B的波形如图中所示。

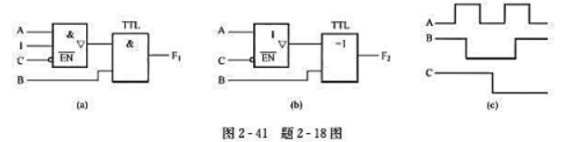

信号波形时,断出F1、F2端的波形。

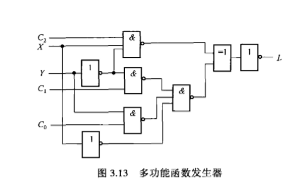

(1)图3.13所示电路是一个多功能函数发生器,其中C2、C1、C0为控制信号,X、Y为数据输入,试列表说明当C2、C1、C0为不同取值组合时,输出端L的逻辑功能(L(X、Y)的表达式).

(2)试改用一个4选1多路数据选择器(1/274LS352)(参见表3.11及图3.14)及最少的门电路实现.上述多功能函数发生器.

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“简答题”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!