题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

参考ASIC的设计流程,判断如下FPGA硬件开发的陈述是否正确。 FPGA的开发代码不需要可综合。 FPGA不

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

抱歉!暂无答案,正在努力更新中……

抱歉!暂无答案,正在努力更新中……

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

抱歉!暂无答案,正在努力更新中……

抱歉!暂无答案,正在努力更新中……

更多“参考ASIC的设计流程,判断如下FPGA硬件开发的陈述是否正确。 FPGA的开发代码不需要可综合。 FPGA不”相关的问题

更多“参考ASIC的设计流程,判断如下FPGA硬件开发的陈述是否正确。 FPGA的开发代码不需要可综合。 FPGA不”相关的问题

B、CPLD的安全性比FPGA高

C、FPGA的集成度比CPLD低

D、一般而言,FPGA的内部资源更为丰富,能够实现更为复杂的逻辑功能

B.在Moore状态机设计中,将状态和输出信号一起编码,达到消除毛刺的目的。例如:用两位二进制表示三个状态,再加上两个输出信号,合起来采用4位状态编码。

C.在Mealy状态机的输出逻辑后加一组输出寄存器,虽然使输出延迟了一个周期,但能有效消除组合逻辑产生的毛刺。

D.当信号在FPGA器件内部通过连线和逻辑门时,一般都有一定的延时,另外信号高低电平转换也需要一定的时间,所以毛刺是不可避免的,不用太在意。

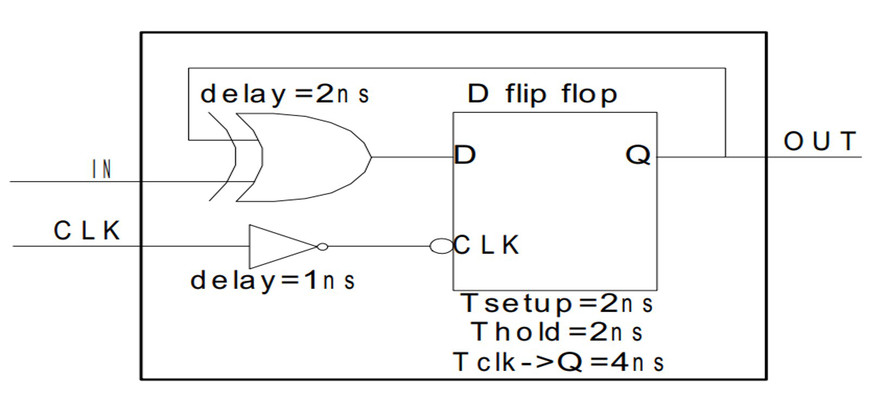

(1)[10分]请问对于flop2,其建立时间裕量为多少? (2)[10分]请问对于flop2,其保持时间裕量为多少?

(1)[10分]请问对于flop2,其建立时间裕量为多少? (2)[10分]请问对于flop2,其保持时间裕量为多少?

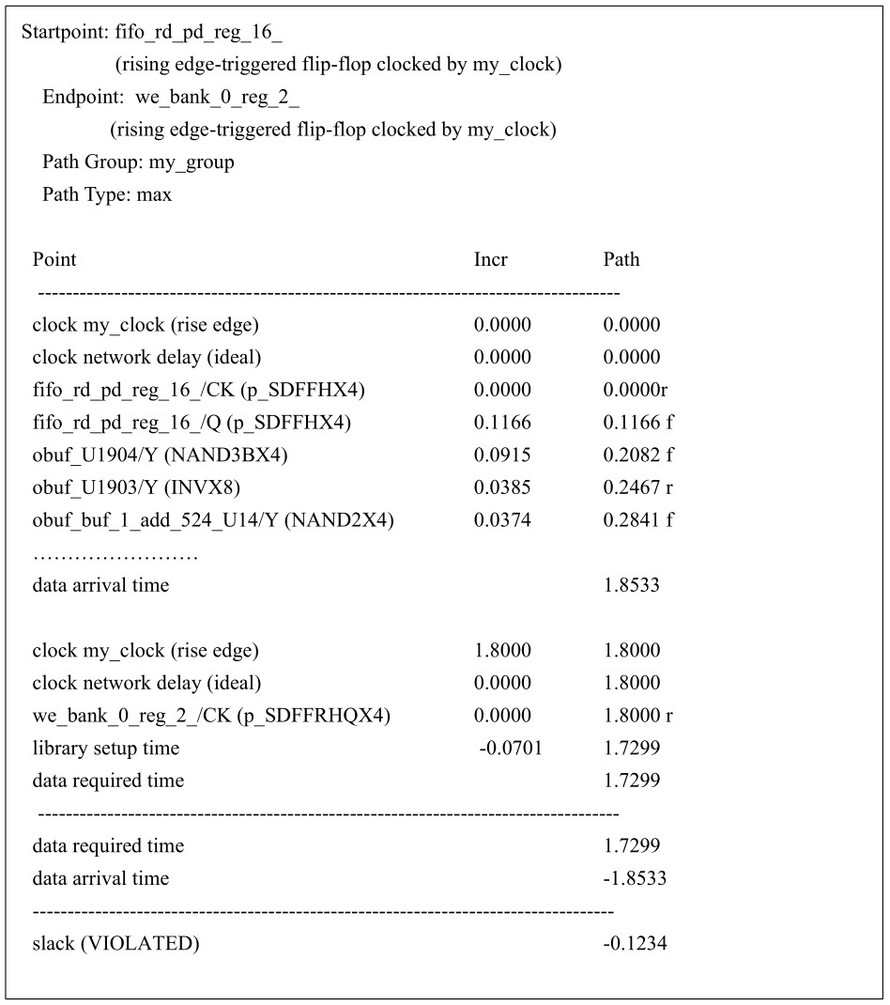

[共20分]根据以下静态时序分析报告回答问题。 (1) 这个报告是哪个EDA工具产生的?[2分] (2) 报告最右侧一列中的“f”和“r”表示什么含义?[2分] (3) 该报告描述的是建立时间还是保持时间? (4) 该电路能跑的最高时钟频率为多少?[4分] (5) 该报告是否能够求出保持时间?[4分] (6) 该报告的数据与芯片布局布线之后的数据是否相同?芯片布局布线阶段与DC综合阶段,在处理时钟网络时有何不同?[4分]

[共20分]根据以下静态时序分析报告回答问题。 (1) 这个报告是哪个EDA工具产生的?[2分] (2) 报告最右侧一列中的“f”和“r”表示什么含义?[2分] (3) 该报告描述的是建立时间还是保持时间? (4) 该电路能跑的最高时钟频率为多少?[4分] (5) 该报告是否能够求出保持时间?[4分] (6) 该报告的数据与芯片布局布线之后的数据是否相同?芯片布局布线阶段与DC综合阶段,在处理时钟网络时有何不同?[4分]

如果把上述电路整体看为一个触发器,请回答如下问题 (1)[20分]该电路的有效建立时间和保持时间是多少?请写出计算过程。 A. Tsetup = 4 ns, Thold = 1 ns B. Tsetup = 3 ns, Thold = 0 ns C. Tsetup = 3 ns, Thold = 1ns D. Tsetup = 2 ns, Thold = 0 ns (2) [20分]该电路的最高时钟频率为多少? 请写出计算过程。 A. 250 MHz B. 80 MHz C. 125 MHz D. 166.7 MHz (3) [10分]该电路的功能与下列哪个触发器相似?[B] A. D flip flop with enable B. T flip flop C. JK flip flop D. SR flip flop (4) [10分]对于一个同步电路,以下哪个公式可以用于计算最高工作频率? A. Max Freq = 1/(Tprop_delay + Tsu + Thold) B. Max Freq = 1/(Tprop_delay + Tsu + Tco + Thold) C. Max Freq = 1/(Tsu + Tco + Thold + Tclock_skew) D. Max Freq = 1/(Tprop_delay + Tsu + Tco + Tclock_skew) E. Max Freq = 1/(Tprop_delay + Tsu + Thold + Tco + Tclock_skew)

如果把上述电路整体看为一个触发器,请回答如下问题 (1)[20分]该电路的有效建立时间和保持时间是多少?请写出计算过程。 A. Tsetup = 4 ns, Thold = 1 ns B. Tsetup = 3 ns, Thold = 0 ns C. Tsetup = 3 ns, Thold = 1ns D. Tsetup = 2 ns, Thold = 0 ns (2) [20分]该电路的最高时钟频率为多少? 请写出计算过程。 A. 250 MHz B. 80 MHz C. 125 MHz D. 166.7 MHz (3) [10分]该电路的功能与下列哪个触发器相似?[B] A. D flip flop with enable B. T flip flop C. JK flip flop D. SR flip flop (4) [10分]对于一个同步电路,以下哪个公式可以用于计算最高工作频率? A. Max Freq = 1/(Tprop_delay + Tsu + Thold) B. Max Freq = 1/(Tprop_delay + Tsu + Tco + Thold) C. Max Freq = 1/(Tsu + Tco + Thold + Tclock_skew) D. Max Freq = 1/(Tprop_delay + Tsu + Tco + Tclock_skew) E. Max Freq = 1/(Tprop_delay + Tsu + Thold + Tco + Tclock_skew)

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“简答题”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!