题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

3/8线译码器,若译码器为输出高电平有效,若输入为A2A1A0=011时,输出Y7Y6Y5Y4Y3Y2Y1Y0为()

A.11110111

B.00001000

C.11111011

D.00000100

参考答案

参考答案

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

网友提供的答案

网友提供的答案

- · 有3位网友选择 A,占比37.5%

- · 有3位网友选择 C,占比37.5%

- · 有2位网友选择 B,占比25%

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.11110111

B.00001000

C.11111011

D.00000100

参考答案

参考答案

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

网友提供的答案

网友提供的答案

更多“3/8线译码器,若译码器为输出高电平有效,若输入为A2A1A0=011时,输出Y7Y6Y5Y4Y3Y2Y1Y0为()”相关的问题

更多“3/8线译码器,若译码器为输出高电平有效,若输入为A2A1A0=011时,输出Y7Y6Y5Y4Y3Y2Y1Y0为()”相关的问题

对于74LS194,当处于并行输入功能时,第9引脚和第10引脚

应为

应为

A、 =1,

=1, =0

=0

B、 =1,

=1, =1

=1

C、 =0,

=0, =0

=0

D、 =0,

=0, =1

=1

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计3线-8线译码器CT74138电路,建立CT74138的实验模式。通过电路仿真和硬件验证,进一步了解3线-8线译码器的功能和特性。

设计原理

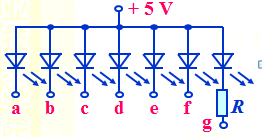

3线-8线译码器CT74138的元件符号如图所示,3线地址输入端为C、B和A;8线译码输出端为Y7N~Y0N,低电平有效;G1、G2AN和G2BN是使能控制输入端,当G1、G2AN和G2BN为1、0和0时,译码器工作,当它们不是“100”时,译码器被禁止工作,全部输出均为无效电平(高电平“1”)。

已知74LS138译码器的输入三个使能端( =1,

=1, =

= =0)时,地址码

=0)时,地址码 =111,则对应的输出为0的是( )。

=111,则对应的输出为0的是( )。

A、

B、

C、

D、

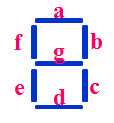

显示 字形 十六进制数 dp g f e d c b a 0 C0 1 1 0 0 0 0 0 0 1 6 A L

显示 字形 十六进制数 dp g f e d c b a 0 C0 1 1 0 0 0 0 0 0 1 6 A L

A、01

B、F9

C、10

D、06

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“简答题”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!