题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

衬源短接的增强型NMOSFET,VDS>0正常开启时,衬底表面电势最低点出现在_______

A.源区

B.沟道区靠近源区一侧

C.沟道区靠近漏区一侧

D.漏区

参考答案

参考答案

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

网友提供的答案

网友提供的答案

- · 有4位网友选择 B,占比40%

- · 有3位网友选择 C,占比30%

- · 有2位网友选择 D,占比20%

- · 有1位网友选择 A,占比10%

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.源区

B.沟道区靠近源区一侧

C.沟道区靠近漏区一侧

D.漏区

参考答案

参考答案

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

简答题官方参考答案

(由简答题聘请的专业题库老师提供的解答)

网友提供的答案

网友提供的答案

更多“衬源短接的增强型NMOSFET,VDS>0正常开启时,衬底表面电势最低点出现在_______”相关的问题

更多“衬源短接的增强型NMOSFET,VDS>0正常开启时,衬底表面电势最低点出现在_______”相关的问题

B、VDS=2V时,漏端沟道厚度比源端厚,但相差不大可近似看成均匀

C、VDS从2V变为4V时,源端沟道越来越薄,IDS随VDS上升减慢

D、VDS=4V时,沟道进入夹断的临界状态,MOS管由导通变为截止

B、当VGS=0,NMOS倒相器处于截止状态,VDS接近VDD

C、当NMOS管导通时,输出电压VD下降

D、管子工作于截止与导通两个状态,故倒相器起了开关的作用

A、(1/4)Is

B、(1/2)Is

C、2Is

D、4Is

B、空穴,由漏端到源端

C、电子,由源端到漏端

D、电子,由漏端到源端

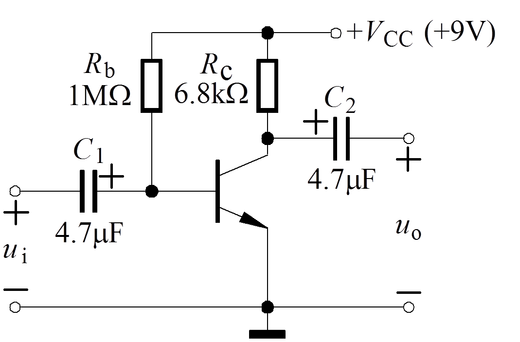

已知图示电路中晶体管 =100,rbe=3.3k

=100,rbe=3.3k 。该放大电路的中频电压放大倍数

。该放大电路的中频电压放大倍数 约为____(A、50, B、100, C、200);下限截止频率fL约为____Hz。(A、1, B、10, C、100);当 Ui=7mV,f=fL时,Uo约为 ____V(A、0.1, B、0.7, C、1, D、1.4)。

约为____(A、50, B、100, C、200);下限截止频率fL约为____Hz。(A、1, B、10, C、100);当 Ui=7mV,f=fL时,Uo约为 ____V(A、0.1, B、0.7, C、1, D、1.4)。

A、CBC

B、ABC

C、ABA

D、ACB

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“简答题”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!